「半導体集積回路の密度が2年ごとに倍増する」という半導体のイノベーションの成長速度を予測した「ムーアの法則」は、近いうちに終焉を迎えると言われています。この法則を提唱したIntelの創業者の1人であるゴードン・ムーア氏も「トランジスタが原子レベルまで小さくなり限界に達する」と述べているのですが、主要な半導体メーカーは2020年までに「EUVリソグラフィ」の実用化を進めており、数年以内にムーアの法則の限界を回避できる可能性が出てきています。

Leading Chipmakers Eye EUV Lithography to Save Moore’s Law - IEEE Spectrum

http://spectrum.ieee.org/semiconductors/devices/leading-chipmakers-eye-euv-lithography-to-save-moores-law

半導体の回路をウェハー上に製造する際の配線の幅を「プロセスルール」と呼び、最小加工寸法によってCPUが「14nm世代」「22nm世代」と分類されるのですが、次世代の「10nm世代」は開発が大幅に遅れており、Intelの10nmプロセス採用製品「Cannonlake」も登場が2017年になる見通しです。そこで最先端のプロセッサを製造するための技術として、主要な半導体メーカーが注目している「EUVリソグラフィ」と呼ばれる技術が実用化されれば、ムーアの法則に基づいた開発スケジュールが立つと見られています。

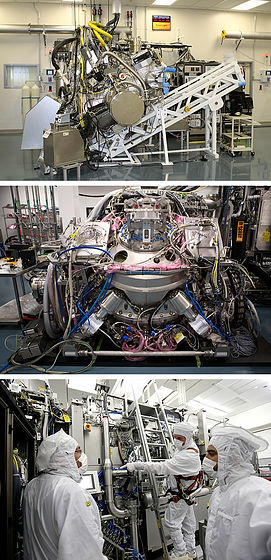

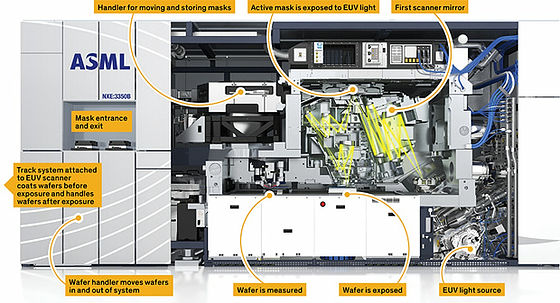

EUVリソグラフィは極端紫外線という非常に短い波長のレーザー光線を用いたリソグラフィ技術で、従来の技術では加工が難しい20nm以下の寸法で半導体の加工が可能になり、実用化されれば集積回路部品の密度は2倍以上になるとされています。13.5nmという短波長のEUV光はプラズマから取り出すことで十分な輝度(強度)を得ることができ、X線や粒子加速器を使う方法よりも実用的かつ経済的とされています。

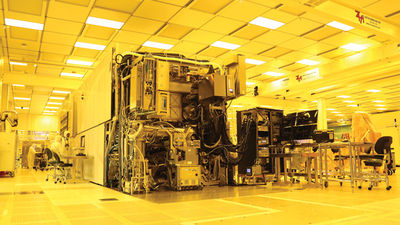

EUVリソグラフィのレーザーを実用化するには250ワット以上の出力を維持する必要があるのですが、2016年初頭にはオランダの半導体製造メーカー・ASMLが研究所環境ではあるものの、プレパルス方式を利用して200ワットの出力を達成したことを報告しています。

EUVリソグラフィを製造ラインに組み込むのはそう遠くない未来に迫りつつあり、2018年にはIntelとTSMCがEUVリソグラフィを実用化できる見込みがあるとのこと。GlobalFoundriesは2018年に「7nm世代」の製造をEUVリソグラフィなしで計画していますが、準備が完了次第EUVを組み込む予定とのこと。さらに「5nm世代」の製造ラインの場合、TSMCが2020年にEUVリソグラフィを採用する見込みです。