はじめに

Rubin Ultra の HBM の数ですが、

の時に発表されたときは、12でした。

では、なんで、HBM の数が 12 から 16 になったのでしょうか?

これについて、今回も妄想したいと思います。

それでは、

Let's 妄想

Rubin Ultran

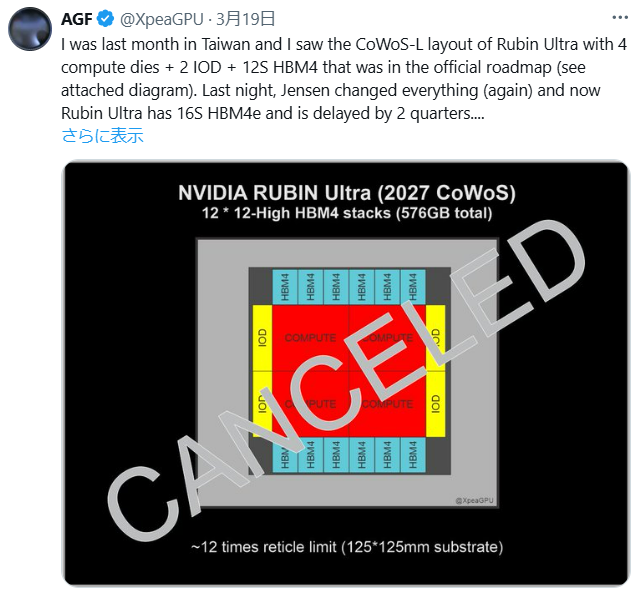

下記のXの投稿では、下記のような図が載っていました。

I was last month in Taiwan and I saw the CoWoS-L layout of Rubin Ultra with 4 compute dies + 2 IOD + 12S HBM4 that was in the official roadmap (see attached diagram). Last night, Jensen changed everything (again) and now Rubin Ultra has 16S HBM4e and is delayed by 2 quarters....… pic.twitter.com/NYSq9SzotB

— AGF (@XpeaGPU) 2025年3月19日

投稿が無くなると、後で参照できないので、魚拓を取りました。

図の下の方に、~ 12 times reticle limit (125 * 125 mm substrate)

とあります。

これ、TSMCのCoWoSの図と似ています。下記のブログでも引用しました。

引用した図を下記に示します。今回も説明のために引用します。

Blackwell、Blackwell Ultra、Rubin までは、CoWoS (3.3-ret.) になると思います。

12 x HBM だと、

- 2026 : CoWoS 5.5-ret.

- 2027 : CoWoS 8-ret.

になります。

Rubin を CoWoS 3.3 ret. で実装したため、大きな変更無しに Rubin Ultra を実現するには、上記の CoWoS 5.5-ret. / 8-ret. は採用できません。

上記のXの投稿が事実であるのなら、TSMCのCoWoSの Roadmap に合わせて、CoWoS 8-ret. にて実装していると思います。

CoWoS 8-ret. になると、Compute Die は 2種類開発することになります。また、Die 間の接続が2箇所になりますね。

Blackwell => Blackwell Ultra => Rubin に流れからちょっと違うため、色々なところで新しい問題にぶつかったのかもしれません。

おわりに

TSMCのCoWoS。5.5-ret. までは、従来までの延長線で実装できたのかもしれませんが、8-ret. はちょっと変わってきた。それに大きな影響を受けるものは大変になる?ということでしょうか?

ということで、今回はここまでで、

次回も Let's 妄想

追記)、2025.03.29

Rubin Ultra の画像を再度見直したら、左右がミラーになっているように見えます。

ということは、これは、あくまでも暫定版なのだろうか?

あれ、NVIDIA Rubin Ultra

— Vengineerの妄想 (@Vengineer) 2025年3月29日

左右がミラーになっているように見えるけど。 pic.twitter.com/L4Pl945vf2