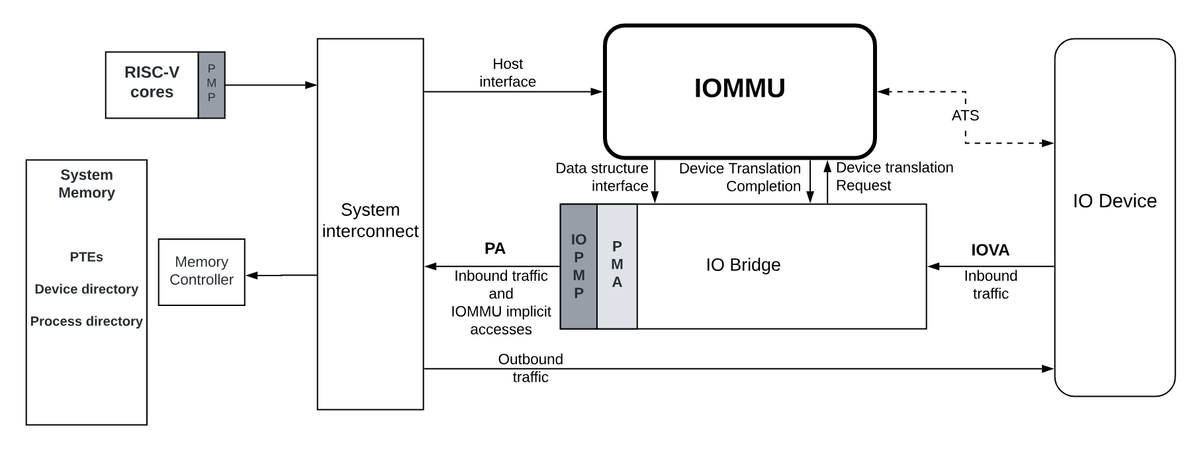

次に、IOMMUが実際のシステム内でどのように使われるのか、仕様書に含まれる図を眺めながら見てみよう。

下記の図には、大きく分けて以下の重要なコンポーネントが含まれている。

- RISC-V Cores: RISC-V CPU自体である。

- IOデバイス: IO Device AとIO Device Bが相当する。AIアクセラレータなどの、ハードウェアデバイスだと考えればよい。

- PCIe Rootポート: PCIeデバイスのためのルートポート

- IOMMU0 / IOMMU1: IOMMU本体である

- IO Bridge: IOMMUに接続されており、IOデバイスやルート・ポートからのIOVAリクエストをIOMMUを介してPAに変換する。

上記で説明した通り、IO DeviceやPCIe ルート・ポートが生成するIOVAを、IO BridgeおよびIOMMUを介してSystem Interconnectに接続されている。

下側のIOMMU1およびIO Bridge1については、ルート・ポートを使用せずにIO Device AとIO Device BをSystem Interconnectに接続している。

IOMMUのインタフェース

IOMMUには、いくつかのインタフェースが接続されている。

- Host Interface: グローバル・コンフィギュレーションやメンテナンスを行うためのインタフェース。System Interconnectからメモリ・マップされており、RISC-V Coresなどからコンフィグレーションを行うためのインタフェースである。

- Data Translation Request: IOデバイスなどからのIOVAのアドレスを、IO Bridgeを介して変換する要求を受け取るためのインタフェース

- Data Translation Complete: 上記のリクエストの変換完了を通知するためのインタフェース

- Data Structure Interface: IO Bridgeに渡っているが、実際にはメインメモリにアクセスを行うためのインタフェースであり、アドレス変換に必要な情報をメインメモリから取得するために使用する。

- ATS Interface: オプションのPCIeATS機能がIOMMUでサポートされている場合に使用される。ATSはAddress Translation Serviceの略であり、PCIe自体が持っているアドレス変換の仕組みである。