HPCA2024で開催された、RISC-Vのアウト・オブ・オーダCPU XiangShanについての資料が公開されていたので、読んでみることにした。 じっくり読みたいので、1ページずつ要点を抑えていく。

次は、マイクロアーキテクチャのトピックについて。

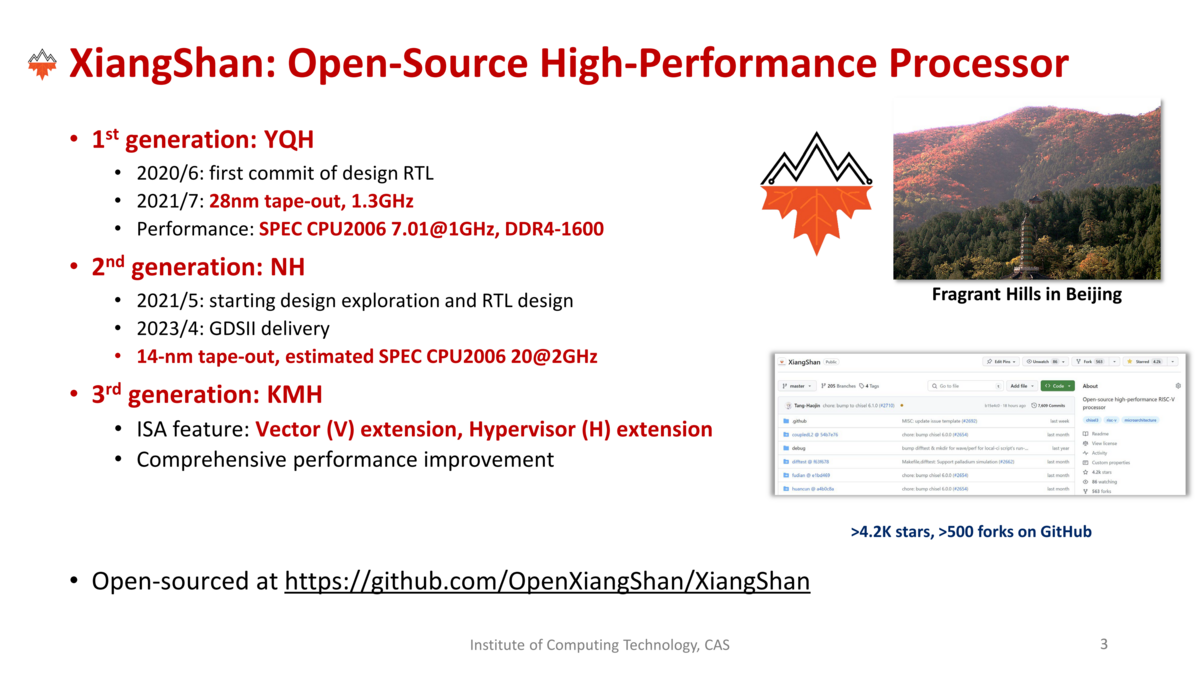

XiangShanには3つの世代がある。

- YQH : 28nm でテープアウトし1.3GHz。性能的にはSPEC CPU2006 7.01 @1GHz

- NH : 14nmでテープアウトし2.0GHz。性能的にはSPEC CPU2006 20 @2GHz

- KMH : Vector拡張とハイパーバイザー拡張を実装。

- まずは第1世代のYQHについて。

- 11ステージの6命令デコード・リネーム

- TAGE-SC-Lの分岐予測器を実装

- 整数物理レジスタ160エントリ、浮動小数点物理レジスタ160エントリ

- 192エントリのROB、64エントリのLQ、48エントリのSQ

- 各機能ユニットには16エントリのRS

- 16KBのL1命令キャッシュ、128KBのL1plus命令キャッシュ

- 32KBのL1データキャッシュ

- 32エントリのITLB / DTLB, 4KエントリのSTLB

- 1MBのインクルーシブ・L2キャッシュ

- YQHのマイクロアーキテクチャ(パイプライン)

- ディスパッチするときにレジスタを読むスタイル。14Read / 8Write

- 最大コミット数は6命令/1サイクル

- 第2世代、NHのアーキテクチャ

- 整数物理レジスタ196エントリ、浮動小数点物理レジスタ192エントリに増強

- ROBは256エントリに増強、80エントリのLQ、64エントリのSQに増強

- 算術演算ユニットは各32エントリのRS

- 64KBのL1命令キャッシュ

- 64KBのL1データキャッシュ

- 80エントリのDTLB、32エントリのITLB、2KエントリのSTLB

- 1MBのノン・インクルーシブL2キャッシュ

- 6MBのノン・インクルーシブL3キャッシュ

- NHのフロントエンド

- フロントエンドをProducerとConsumerに分離。

- Producer : 分岐予測ユニット

- Consumer : 命令フェッチユニット

- フロントエンドをProducerとConsumerに分離。

- 分岐予測について

- 3ステージの分岐予測

- ステージ1: uBTB

- ステージ2: FTB + TAGE (FTB : Fetch Target Bufferのこと)

- ステージ3: SC + ITAGE + RAS (SCは良く分からないが、Statistical Correctorのこと?)

- 3ステージの分岐予測

- 命令キャッシュ

- 64KBの4-way VIPTブロッキングキャッシュ

- TileLinkをサポート

- PLRUのリプレースメント